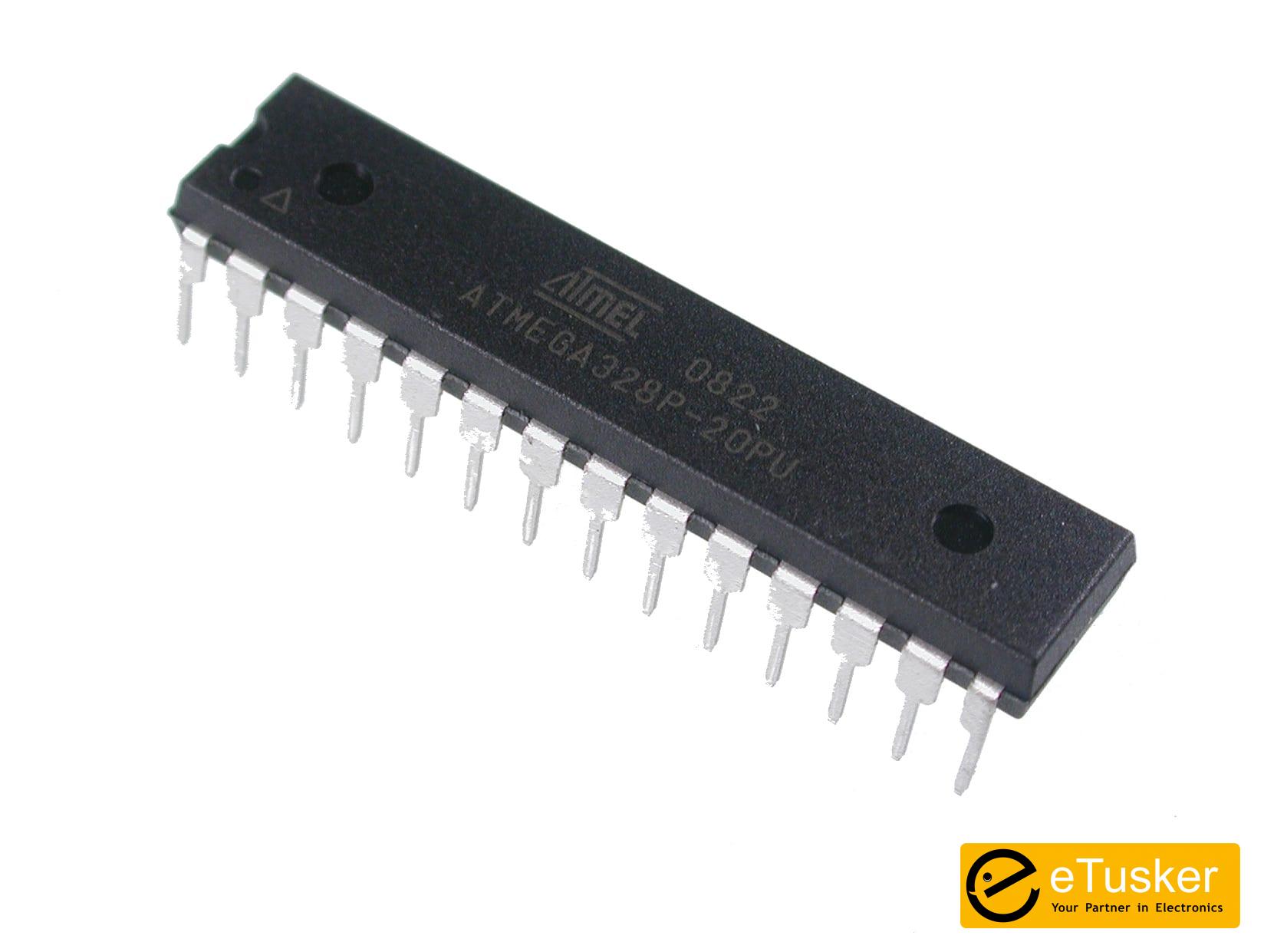

Atmega32A-PU-PDIP

The low power, high performance Microchip 8-bit AVR RISC-based microcontroller featuring 32KB self-programming flash program memory, 2KB SRAM, 1KB EEPROM, 8 channel 10-bit A/D converter and JTAG interface for on-chip-debug. The device acheives 16 MIPS throughput at 16 MHz at 2.7-5.5V operation.

By executing powerful instructions in a single clock cycle, the device achieves throughputs approaching 1 MIPS per MHz, allowing you to optimize power consumption versus processing speed.

-

- Advanced RISC Architecture

- 131 Powerful Instructions – Most Single-clock Cycle Execution

- 32 × 8 General Purpose Working Registers

- Fully Static Operation

- Up to 16MIPS Throughput at 16MHz

- On-chip 2-cycle Multiplier

- High Endurance Non-volatile Memory segments

- 32Kbytes of In-System Self-programmable Flash program memory

- 1024Bytes EEPROM

- 2Kbytes Internal SRAM

- Write/Erase cycles: 10,000 Flash/100,000 EEPROM

- Data retention: 20 years at 85°C/100 years at 25°C

- Optional Boot Code Section with Independent Lock Bits

- In-System Programming by On-chip Boot Program

- True Read-While-Write Operation

- Programming Lock for Software Security

- JTAG (IEEE std. 1149.1 Compliant) Interface

- Boundary-scan Capabilities According to the JTAG Standard

- Extensive On-chip Debug SupportProgramming of Flash, EEPROM, Fuses and Lock Bits through the JTAG Interface

-

- QTouch library support

- Capacitive touch buttons, sliders and wheels

- QTouch and QMatrix acquisition

- Up to 64 sense channels

- Advanced RISC Architecture

The low power, high performance Microchip 8-bit AVR RISC-based microcontroller featuring 32KB self-programming flash program memory, 2KB SRAM, 1KB EEPROM, 8 channel 10-bit A/D converter and JTAG interface for on-chip-debug. The device acheives 16 MIPS throughput at 16 MHz at 2.7-5.5V operation.

By executing powerful instructions in a single clock cycle, the device achieves throughputs approaching 1 MIPS per MHz, allowing you to optimize power consumption versus processing speed.

-

- Advanced RISC Architecture

- 131 Powerful Instructions – Most Single-clock Cycle Execution

- 32 × 8 General Purpose Working Registers

- Fully Static Operation

- Up to 16MIPS Throughput at 16MHz

- On-chip 2-cycle Multiplier

- High Endurance Non-volatile Memory segments

- 32Kbytes of In-System Self-programmable Flash program memory

- 1024Bytes EEPROM

- 2Kbytes Internal SRAM

- Write/Erase cycles: 10,000 Flash/100,000 EEPROM

- Data retention: 20 years at 85°C/100 years at 25°C

- Optional Boot Code Section with Independent Lock Bits

- In-System Programming by On-chip Boot Program

- True Read-While-Write Operation

- Programming Lock for Software Security

- JTAG (IEEE std. 1149.1 Compliant) Interface

- Boundary-scan Capabilities According to the JTAG Standard

- Extensive On-chip Debug SupportProgramming of Flash, EEPROM, Fuses and Lock Bits through the JTAG Interface

-

- QTouch library support

- Capacitive touch buttons, sliders and wheels

- QTouch and QMatrix acquisition

- Up to 64 sense channels

- Advanced RISC Architecture